某项目的CISCO产品测试报告之实验一、设备接口测试

1. 实验项目: 端口类型 -千兆以太口、快速以太口、POS 155M 口、2 兆口

确认参加测试的设备、接口类型及参加测试的软件类型。

a. 验证接口类型为:

千兆以太口

快速以太口

POS 155M 口

2 兆口

b. 正式发布的软件为:

12.0.22S

2. 实验方法:

进行现场实地考察、并用命令考察版本。

3. 环境

三台骨干路由器、三台接入路由器、两台三层接入交换机、一台二层交换机

4. 实验设备

7513 两台、Cisco 7507 一台、Cisco 7206 一台、Cisco 3640 两台、Catalyst 4006 两台、Catalyst 6509 一台、千兆卡三块、POS-155M卡两台、快速以太卡若干、串口卡若干。

5. 测试版本

IOS 正式版本 12.0.22S

6. 校验命令

Show ip interface brief

R1#sh ip inter bri

Interface IP-Address OK? Method Status Protocol

FastEthernet2/0/0 10.10.15.1 YES NVRAM up up

FastEthernet2/0/1 10.10.15.1 YES NVRAM up up

POS4/0/0 10.10.13.1 YES NVRAM up up

Serial4/1/0 unassigned YES NVRAM up down

Serial4/1/1 unassigned YES NVRAM up up

Serial4/1/2 unassigned YES NVRAM up up

Serial4/1/3 unassigned YES NVRAM up down

FastEthernet10/0/0 unassigned YES unset administratively down down

FastEthernet10/0/1 unassigned YES unset administratively down down

Multilink1 10.10.12.1 YES NVRAM up up

Loopback0 10.10.10.1 YES NVRAM up up

R1#

R2#sh ip inter bri

Interface IP-Address OK? Method Status Protocol

FastEthernet8/0/0 10.10.26.2 YES NVRAM up up

Serial8/1/0 unassigned YES NVRAM up up

Serial8/1/1 unassigned YES NVRAM up up

Serial8/1/2 unassigned YES NVRAM up up

Serial8/1/3 unassigned YES NVRAM administratively down down

FastEthernet9/0/0 10.10.22.2 YES NVRAM up up

Serial9/1/0 unassigned YES NVRAM up down

Serial9/1/1 unassigned YES NVRAM up up

Serial9/1/2 unassigned YES NVRAM up up

Serial9/1/3 unassigned YES NVRAM up down

GigabitEthernet10/0/0 10.10.23.2 YES NVRAM up up

GigabitEthernet11/0/0 unassigned YES unset administratively down down

Multilink1 10.10.12.2 YES NVRAM up up

Multilink2 10.10.26.2 YES NVRAM up up

Loopback0 10.10.20.2 YES NVRAM up up

R2#

R3#sh ip inter bri

Interface IP-Address OK? Method Status Protocol

FastEthernet0/0/0 unassigned YES unset administratively down down

FastEthernet0/0/1 unassigned YES unset administratively down down

GigabitEthernet1/0/0 10.10.23.3 YES NVRAM up up

FastEthernet4/0/0 10.10.33.3 YES NVRAM up up

FastEthernet4/0/1 unassigned YES NVRAM administratively down down

POS5/0/0 10.10.13.2 YES NVRAM up up

Loopback0 10.10.30.3 YES NVRAM up up

R3#

Show Version

R1#sh ver

Cisco Internetwork Operating System Software

IOS (tm) RSP Software (RSP-PV-M), Experimental Version 12.1(20020503:125348) [mssunil-cosmos_e_latest 102]

Copyright (c) 1986-2002 by cisco Systems, Inc.

Compiled Fri 03-May-02 21:47 by mssunil

Image text-base: 0x60010958, data-base: 0x611A6000

ROM: System Bootstrap, Version 12.0(20011126:200409) [mssunil-RSP16_BENGAL_120S 251], DEVELOPMENT SOFTWARE

R1 uptime is 48 minutes

System returned to ROM by reload at 13:21:28 UTC Sat Jan 22 2000

System image file is "bootflash:rsp-pv-mz.cosmos_e_latest"

cisco RSP16 (R7000A) processor with 262144K/8216K bytes of memory.

R7000 CPU at 400Mhz, Implementation 39, Rev 3.3, 256KB L2, 2048KB L3 Cache

Last reset from power-on

G.703/E1 software, Version 1.0.

G.703/JT2 software, Version 1.0.

X.25 software, Version 3.0.0.

Chassis Interface.

1 VIP6 RM7000B controller (2 FastEthernet).

2 VIP2 R5K controllers (2 FastEthernet)(4 Serial)(1 POS).

4 FastEthernet/IEEE 802.3 interface(s)

4 Serial network interface(s)

1 Packet over SONET network interface(s)

2043K bytes of non-volatile configuration memory.

20480K bytes of Flash PCMCIA card at slot 0 (Sector size 128K).

16384K bytes of Flash internal SIMM (Sector size 256K).

Slave in slot 7 is running Cisco Internetwork Operating System Software

IOS (tm) RSP Software (RSP-DW-M), Experimental Version 12.1(20020503:125348) [mssunil-cosmos_e_latest 103]

Copyright (c) 1986-2002 by cisco Systems, Inc.

Compiled Fri 03-May-02 22:01 by mssunil

Slave: Loaded from system

Slave: cisco RSP16 (R7000A) processor with 262144K bytes of memory.

Configuration register is 0x2102

R2#sh ver

Cisco Internetwork Operating System Software

IOS (tm) RSP Software (RSP-PV-M), Version 12.0(22)S, EARLY DEPLOYMENT RELEASE SOFTWARE (fc2)

TAC Support: http://www.cisco.com/tac

Copyright (c) 1986-2002 by cisco Systems, Inc.

Compiled Sat 20-Jul-02 01:33 by nmasa

Image text-base: 0x60010B38, data-base: 0x61016000

ROM: System Bootstrap, Version 11.1(8)CA1, EARLY DEPLOYMENT RELEASE SOFTWARE (fc1)

BOOTLDR: RSP Software (RSP-BOOT-M), Version 12.1(5a), RELEASE SOFTWARE (fc1)

R2 uptime is 1 hour, 3 minutes

System returned to ROM by reload at 01:50:44 UTC Wed Sep 18 2002

System image file is "disk0:rsp-pv-mz.120-22.S.bin"

cisco RSP4 (R5000) processor with 262144K/2072K bytes of memory.

R5000 CPU at 200Mhz, Implementation 35, Rev 2.1, 512KB L2 Cache

Last reset from power-on

G.703/E1 software, Version 1.0.

G.703/JT2 software, Version 1.0.

X.25 software, Version 3.0.0.

Chassis Interface.

2 GEIP controllers (2 GigabitEthernet).

1 VIP2 controller (1 FastEthernet)(4 Serial).

1 VIP2 R5K controller (1 FastEthernet)(4 Serial).

2 FastEthernet/IEEE 802.3 interface(s)

2 GigabitEthernet/IEEE 802.3 interface(s)

8 Serial network interface(s)

123K bytes of non-volatile configuration memory.

125952K bytes of ATA PCMCIA card at slot 0 (Sector size 512 bytes).

8192K bytes of Flash internal SIMM (Sector size 256K).

Slave in slot 7 is running Cisco Internetwork Operating System Software

IOS (tm) RSP Software (RSP-DW-M), Version 12.0(22)S, EARLY DEPLOYMENT RELEASE SOFTWARE (fc2)

TAC Support: http://www.cisco.com/tac

Copyright (c) 1986-2002 by cisco Systems, Inc.

Compiled Sat 20-Jul-02 01:48 by nmasa

Slave: Loaded from system

Slave: cisco RSP4 (R5000) processor with 262144K bytes of memory.

Configuration register is 0x2102

R3#sh ver

Cisco Internetwork Operating System Software

IOS (tm) RSP Software (RSP-PV-M), Version 12.0(22)S, EARLY DEPLOYMENT RELEASE SOFTWARE (fc2)

TAC Support: http://www.cisco.com/tac

Copyright (c) 1986-2002 by cisco Systems, Inc.

Compiled Sat 20-Jul-02 01:33 by nmasa

Image text-base: 0x60010B38, data-base: 0x61016000

ROM: System Bootstrap, Version 11.1(8)CA1, EARLY DEPLOYMENT RELEASE SOFTWARE (fc1)

BOOTLDR: RSP Software (RSP-PV-M), Version 12.0(22)S, EARLY DEPLOYMENT RELEASE SOFTWARE (fc2)

R3 uptime is 54 minutes

System returned to ROM by reload at 01:23:37 UTC Wed Sep 18 2002

System image file is "slot0:rsp-pv-mz.120-22.S.bin"

cisco RSP4 (R5000) processor with 163840K/2072K bytes of memory.

R5000 CPU at 200Mhz, Implementation 35, Rev 2.1, 512KB L2 Cache

Last reset from p

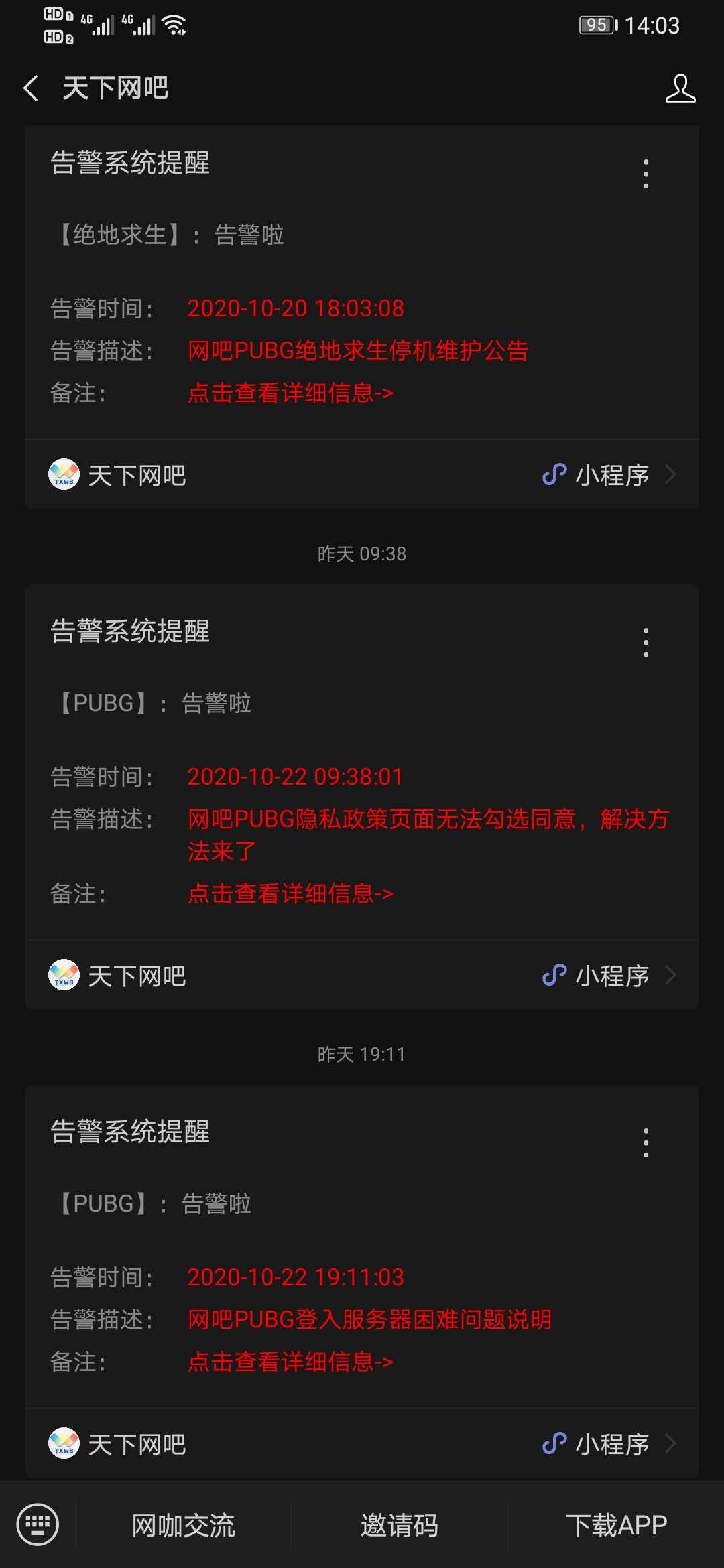

天下网吧・网吧天下

天下网吧・网吧天下