Tegra 4/4i、Icera i500架构深度解析

CES 2013大展上,NVIDIA发布了全球首款四核A15架构移动处理器“Tegra 4”(代号Wayne),伴随而来的是4G/LTE基带“Icera i500”。MWC 2013大会上,NVIDIA又带来了整合基带的“Tegra 4i”(代号Grey),同样四核心,但架构上基于Cortex-A9,而所用基带正是Icera i500。

AnandTech近日撰文,深度解析了Tegra 4、Icera i500、Tegra 4i的硬件架构设计,还有部分性能数据。感兴趣的随我来。

【Tegra 4:A15架构细节、功耗控制】

NVIDIA其实是ARM指令集架构的授权拥有者,但这一次,Tegra 4使用的还是处理器授权,而不是NVIDIA自己设计的定制核心(就像高通Krait、苹果Swift那样的),那要到“丹佛工程”上才能实现。

对于A15的架构情况,之前因为资料有限,我们了解得并不多,而得益于Tegra 4的白皮书等文档,终于可以一窥A15内部世界了。更深入的解析会有机会单独阐述,这里只从较高层面上看看。

A15的架构要比A9宽得多、深得多,整数流水线也从9级增加到了15级,但是分支预测同样改进显著,但愿能比弥补长流水线的缺憾。

A15的前端宽了50%,指令拾取带宽翻番,有利于提升指令级并行(ILP),而为了充分利用三宽度发射,ARM大大增加了重排序缓冲(ROB)和所有相关数据结构的尺寸。A9可以在重排序缓冲内保留大约32-40个已解码指令,A15则能保留128个,仅此一点就足以反映两种架构的巨大差异:A9是基于A8的自然演化,A15则是一次全新的飞跃式革命。

执行核心方面,A15的规模仍然更大,执行端口、执行单元都要比A9的多,均有助于提升ILP、单线程性能,还采用了多重、独立的发射队列的方式,以保持高频率。每一个发射队列都可以接受最多三条指令,所有的发射队列都可以并行分发。

A15也可以执行乱序指令,但能力更强了。A9上所有的浮点/NEON指令都必须顺序执行,但在A15上可以乱序,但是它依然不能重排序所有内存操作:独立载入可以乱序执行,但是存储不能在载入之前完成。

A15还改用了集成式二级缓存结构,而不是A9上的独立IP块。A15的一级、二级缓存延迟基本没变,不过在一些情况下应该会比A9多上1-2个时钟周期。二级缓存TLB和其它数据结构明显增大,以满足整个架构的需要。

缓存容量上,一级还是32KB指令、32KB数据,但是二级增至2MB,并为所有核心共享(Tegra 4的第五个节能核心还有自己的512KB二级缓存),任何核心只要允许都可以单独占用全部2MB二级缓存。

A15是目前唯一可以在性能上超越当今流行A9核心的ARM架构,不过性能也不菲。根据三星最新公布的数据,A15可以提供最多3倍于A9的性能,但核心面积要达到4倍,功耗则要付出6倍。面积还好说,功耗就是大麻烦了。

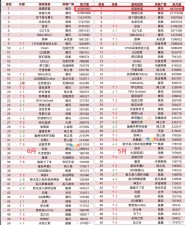

而为了让大家对新架构的功耗放心,NVIDIA给出了这么一张图:

更多执行资源以提升ILP、更多的乱序利用、更好地内存子系统以提升内存级并行(MLP)、更智能的分支预测、平衡的移动应用功耗……这些都是说A15架构的功耗控制特性的,而下方两行展示了Tegra 3、Tegra 4的功耗对比。

NVIDIA宣称,SPECint2000测试(可充分压榨CPU资源)中Tegra 4/3的单线程整数成绩是相同的,但是Tegra 4的功耗要低40%,再用性能除以功耗,Tegra 4在能效方面要胜出75%。

不过这样的对比并不太公平,因为此时Tegra 3的频率是最高的1.6GHz,Tegra 4则只有825MHz,电压和功耗自然都低得多。Tegra 4如果全速运行,功耗自然要高得多,虽然性能也会上去,但恐怕能效方面不会太好看。

但这也可能成为Tegra 4用于移动设备时的一种政策:刻意限制频率以控制功耗。而之所以选择825MHz,因为它也是第五个节能专用核心的最高频率,一般时候应该是700-800MHz。

顺便说一句,Tegra 4里的四个主力核心都使用相同的电压和频率层,只是每个核心都可以通过电源栅极单独开关,这和Intel的设计方式差不多,但不如高通每个核心的电压和频率层都是单独的。

说起频率,Tegra 4四个主力核心最高都可达1.9GHz,而如果使用少量核心,可以加速到更高速度,具体如何还得看设备厂商的选择。

【Tegra 4i:A9 r4p1架构最新版】

除了不同架构之间的进化,ARM每一个架构也都有不同的版本,比如说同样是A9,Tegra 2使用的是r1p1,Tegra 3里边是r2p9,Tegra 4i又换成了最新的r4p1。

A9 r4p1架构的GHB、二级缓存TLB、BTAC都增大了三倍,赶上了A15的水平,分别有16K、512、4096,这可以改进分支预测精确度,进一步提升IPC。

数据预取引擎也增强了,包括一个小的一级缓存预取器、单独的缓存预载指令硬件。

NVIDIA宣称,A9 r4p1相比于r2p9可以在SPECint_base测试中获得15%的成绩提升,仅仅是架构微调就获得如此好的整数性能改进着实惊人,当然真实情况如何还不太好说。不管怎样,配合2.3GHz的最高频率,Tegra 4i CPU性能会比Tegra 3好不少。

根据数据,Tegra 5里每个CPU核心的面积为2.7平方毫米,稍大于高通Krait 800,Tegra 4i则仅为1.15平方毫米。单论最大性能,Tegra 4在三者之中最为突出(高通肯定不服),而在性能频率比、性能面积比上,Tegra 4、Tegra 4i分别是最好的。

天下网吧・网吧天下

天下网吧・网吧天下